**KATHOLIEKE UNIVERSITEIT LEUVEN** FAKULTEIT TOEGEPASTE WETENSCHAPPEN DEPARTEMENT ELEKTROTECHNIEK AFDELING ESAT - DIVISIE INSYS Kasteelpark Arenberg 10, B-3001 Leuven, België

#### PARETO-OPTIMIZATION BASED

#### RUN-TIME TASK SCHEDULING

#### FOR EMBEDDED SYSTEMS

Promotoren: Prof. F. CATTHOOR Prof. R. LAUWEREINS Proefschrift voorgedragen tot het behalen van het doctoraat in de toegepaste wetenschappen

door

Peng YANG

September 2004

In samenwerking met  ${}^{\bullet}$

imec vzw

Interuniversitair Micro-Elektronica Centrum Kapeldreef 75 B-3001 Leuven (België)

**KATHOLIEKE UNIVERSITEIT LEUVEN** FAKULTEIT TOEGEPASTE WETENSCHAPPEN DEPARTEMENT ELEKTROTECHNIEK AFDELING ESAT - DIVISIE INSYS Kasteelpark Arenberg 10, B-3001 Leuven, België

#### PARETO-OPTIMIZATION BASED

#### RUN-TIME TASK SCHEDULING

#### FOR EMBEDDED SYSTEMS

Jury : Prof. G. De Roeck, voorzitter Prof. F. Catthoor, promotor Prof. R. Lauwereins, promotor Prof. H. De Man Prof. Y. Berbers Prof. G. Deconinck Prof. H. Corporaal (T.U. Eindhoven)

U.D.C. : 621.39

Proefschrift voorgedragen tot het behalen van het doctoraat in de toegepaste wetenschappen

$\operatorname{door}$

Peng YANG

September 2004

$\bigodot$ 2004 Katholieke Universiteit Leuven - Faculteit Toegepaste Wetenschappen Arenbergkasteel, B-3001 Heverlee (België)

Alle rechten voorbehouden. Niets van deze uitgave mag worden vermenigvuldigd en/of openbaar gemaakt door middel van druk, fotocopie, microfilm, elektronisch of op welke andere wijze ook zonder voorafgaande schriftelijke toestemming van de uitgever.

All rights reserved. No part of this publication may be reproduced in any form by print, photoprint, microfilm, or any other means without written permission from the publisher.

D/2004/7515/81

ISBN 90-5682-541-0

## Acknowledgements

When I am writing down these words, I am looking back into the days and nights of the last five years. Obtaining a Ph.D. is hard work, which is no lack of joys and frustrations. Fortunately, I am not a solitary pilgrim: I am guided and accompanied by my mentors and friends, whom I know I can always turn to, for guidance, discussions, exchanging ideas and support. Hence, at the start of this text, I would like to express my full gratitude to all those who helped me during the last five years.

Prof. Francky Catthoor, for bringing me into the world of embedded systems design, for inspiring and motivating me on the way of research as my promotor. Prof. Rudy Lauwereins, for being my co-promotor and guiding me through all my research. Prof. Hugo De Man and Prof. Yolande Berbers, for being members of the reading committee, for following up my research and for providing invaluable feedbacks. Prof. G. Deconinck and Prof. H. Corporaal, for serving in the jury.

I would like to thank my previous and current group leaders, Diederik Verkest and Johan Vounckx, for providing me with so fantastic an environment to work and study. Thanks to my TCM-mates, Chun Wong, Paul Marchal, Stefaan Himpe, Zhe Ma, Chantal Ykman, Patrick David. I will remember the days we spent together. Thanks to my colleagues in IMEC. I owe them a lot for their generous help and support and for the happy after-hours get-togethers. Dirk Desmet, Shashi Kodamballi, Bingfeng Mei, Prahbat Avasare, Frederik Vermeulen, Miguel Miranda... I can not list all the names but I will keep them in my heart. Also I would like to thank my friends in Leuven and Belgium. They have made my stay here more enjoyable and memorable.

Finally, I would like to thank my family. I know I could never have gone so far if it were not for the support and warm encouragement from them. Also, thanks to my girl friend, for the laughs and dreams she has brought to me.

> Peng Yang Leuven, September 2004

ii

## Abstract

The rapid evolution and convergence of computing, consumer electronics and communication disciplines are witnessing a trend toward integrating complete and complex systems on a single chip. Technology advances lead to platforms with enormous processing capacity that is however not matched with the required increase in system design productivity. One of the most critical bottlenecks is the very dynamic and concurrent behavior of many current multimedia applications. In today's designs, quite conservative worst case timing characteristics are used to cope with this, leading to a partial waste of resources and energy due to over-dimensioning.

In order to deal with these new dynamic applications where tasks and complex data types are created and deleted at run-time based on non-deterministic events, a novel system design paradigm is needed. Our complete Task Concurrency Management methodology first represents and transforms the system into several concurrent partitions with an in-house gray-box model. Then a twophase scheduling approach is proposed to allocate, map and order the tasks and sub-tasks of the system onto the multiprocessor platforms. The designtime scheduler explores the design space per task and stores the exploration results, while the run-time scheduler is used to optimize across all tasks the system performance/cost according to the dynamic system context and the pre-computed task information.

In this thesis, we mainly focus on the algorithms that the run-time scheduler applies to make system-level tradeoffs and the implementation of such a scheduler on top of conventional Real-Time Operating Systems. We have proposed two algorithms for the run-time scheduling. The first algorithm is able to explore the pre-computed design tradeoffs fast, while for systems with more than a few processors, the second algorithm can better exploit the multiprocessor feature and result in better scheduling. To support our two-phase scheduling, a module is developed to provide a generic method to integrate the application, the run-time scheduler and the Real-Time Operating System at low overheads.

The effectiveness of our design methodology has been verified by several real-life demonstrators, both in simulation and on real hardware boards. All results prove our methodology can significantly reduce the system cost at low implementation overheads. iv

# Contents

| 1 Int | roduction                                                 | 1  |

|-------|-----------------------------------------------------------|----|

| 1.1   | Context and Motivation                                    | 1  |

|       | 1.1.1 The System-on-Chip Era                              | 2  |

|       | 1.1.2 Platform Based Design                               | 5  |

|       | 1.1.3 Embedded Software                                   | 7  |

| 1.2   | Two-Phase Task Scheduling: Why and How                    | 9  |

|       | 1.2.1 Design-Time Task Scheduling phase                   | 11 |

|       | 1.2.2 Run-time Task Scheduling Phase                      | 13 |

|       | 1.2.3 Combine Them Together: A Simple Experiment $\ldots$ | 14 |

| 1.3   | Main Contributions                                        | 16 |

| 1.4   | Chapter Overview                                          | 17 |

| Re    | ated Work                                                 | 19 |

| 2.1   | Scheduling Theory                                         | 19 |

|       | 2.1.1 Static Scheduling                                   | 21 |

|       | 2.1.2 Fixed or Dynamic Priority Scheduling                | 21 |

|       | 2.1.3 Dynamic Scheduling                                  | 24 |

|       | 2.1.4 Summary                                             | 27 |

| 2.2   | Low-Power and Cost Considerations                         | 27 |

|       | 2.2.1 Dynamic Power Management                            | 28 |

|       | 2.2.2 Dynamic Voltage Scheduling                          | 28 |

|       | 2.2.3 Battery Life Related                                | 34 |

|       |                                                           |    |

|   |      | 2.2.4   | Physical Implementation of DVS             | 34        |

|---|------|---------|--------------------------------------------|-----------|

|   |      | 2.2.5   | Other Approaches                           | 35        |

|   | 2.3  | Platfo  | rm and Simulation Framework                | 36        |

|   |      | 2.3.1   | System-level Performance and Energy Models | 37        |

|   |      | 2.3.2   | Timing Analysis and Simulation             | 38        |

| 3 | Mo   | del an  | d Methodology                              | 41        |

|   | 3.1  | Overv   | iew of the TCM Flow                        | 41        |

|   | 3.2  | The G   | Fray-box model                             | 42        |

|   | 3.3  | Scenar  | rio Selection                              | 47        |

|   | 3.4  | Two-p   | bhase scheduling                           | 49        |

| 4 | Fast | t and S | Scalable Run-Time Task Scheduling          | 55        |

|   | 4.1  | Motiv   | ational Example                            | 55        |

|   | 4.2  | Run-t   | ime Scheduling Algorithm                   | 59        |

|   |      | 4.2.1   | Application Model                          | 60        |

|   |      | 4.2.2   | Problem Formulation                        | 60        |

|   |      | 4.2.3   | Greedy Heuristic                           | 62        |

|   | 4.3  | Exper   | imental Results                            | 65        |

|   |      | 4.3.1   | Randomly Generated Test Cases              | 65        |

|   |      | 4.3.2   | Real-Life Applications                     | 67        |

|   | 4.4  | Conclu  | usion                                      | 69        |

| 5 | Rui  | n-Time  | e Algorithm for Overlapping Task Schedules | <b>71</b> |

|   | 5.1  | Motiv   | ational Example                            | 71        |

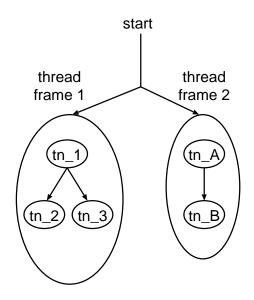

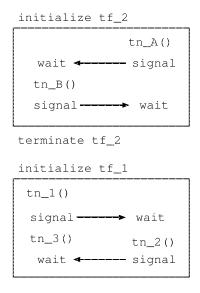

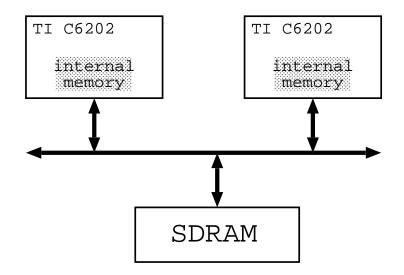

|   |      | 5.1.1   | The Heterogeneous Platform                 | 71        |

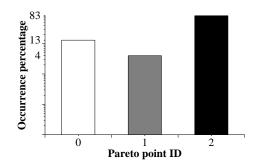

|   |      | 5.1.2   | Design Space Exploration                   | 72        |

|   |      | 5.1.3   | Run-Time Scheduling                        | 73        |

|   | 5.2  | Run-t   | ime Scheduling Heuristic                   | 75        |

|   | 5.3  | Exper   | imental Results                            | 79        |

|   | 5.4  | Concl   | usion                                      | 82        |

vi

| 6            | Vali            | dating | the Methodology with Demonstrators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83                |

|--------------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|              | 6.1             | 3D ren | ndering QoS Control Demonstrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 83                |

|              |                 | 6.1.1  | The QoS Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83                |

|              |                 | 6.1.2  | Virtuoso RTOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85                |

|              |                 | 6.1.3  | Applying the TCM Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 87                |

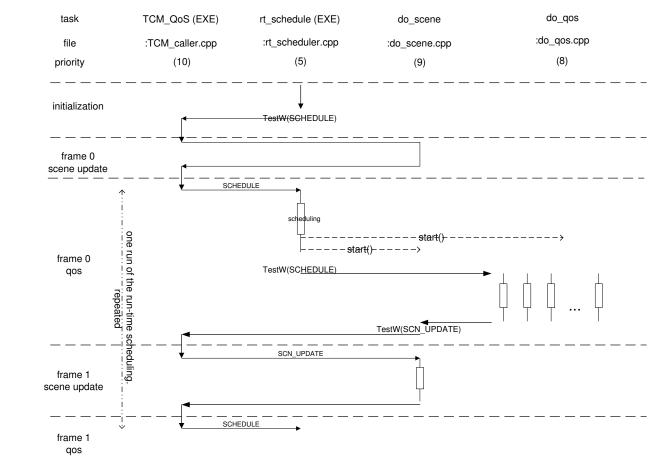

|              |                 | 6.1.4  | $Implementation \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 92                |

|              |                 | 6.1.5  | Reference Cases for Comparison $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95                |

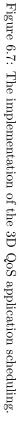

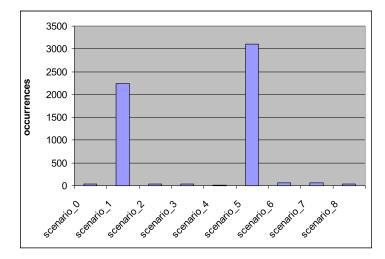

|              |                 | 6.1.6  | Discussion of all results $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96                |

|              | 6.2             | Pocket | tGL Demonstrator on XS<br>cale Board $\hdots \hdots \hdots\hdots \hdots \hdots \hdots \hdots \hdots \hdots \h$ | 97                |

|              |                 | 6.2.1  | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97                |

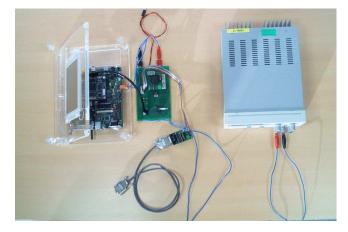

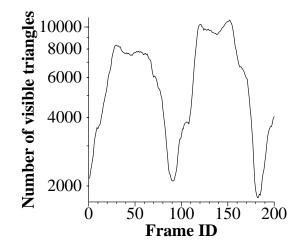

|              |                 | 6.2.2  | Demonstrator Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 99                |

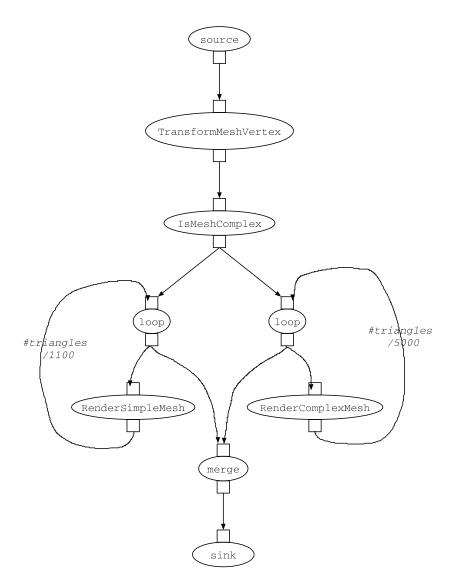

|              |                 | 6.2.3  | Applying the TCM Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 102               |

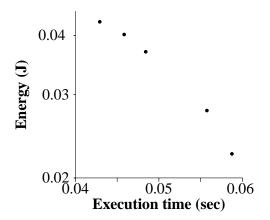

|              |                 | 6.2.4  | Experimental results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 105               |

|              | 6.3             | Conclu | sion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 110               |

| 7            | Ма              | ning   | and Ordening Teaks Dynamically on Multiprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -111              |

| 1            | 7.1             |        | and Ordering Tasks Dynamically on Multiprocessors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 112               |

|              | 7.1<br>7.2      | ,      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 112<br>115        |

|              | 1.2             | 7.2.1  | imental System Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $115 \\ 115$      |

|              |                 | 7.2.1  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\frac{115}{116}$ |

|              | 7.3             |        | The Run-time System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110               |

|              |                 | •      | mentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 121               |

|              | 7.4             | 7.4.1  | iments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\frac{121}{121}$ |

|              |                 | 7.4.2  | The Realistic H.263 Test Case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 121<br>124        |

|              | 7.5             | Conclu |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 124<br>127        |

|              | 1.0             | Concit | 151011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 121               |

| 8            | Con             | clusio | ns and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 129               |

|              | 8.1             | Contri | butions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 130               |

|              | 8.2             | Future | e Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 131               |

| $\mathbf{A}$ | $\mathbf{List}$ | of Pu  | blications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 133               |

vii

#### **B** Abbreviations

135

viii

### Chapter 1

## Introduction

#### 1.1 Context and Motivation

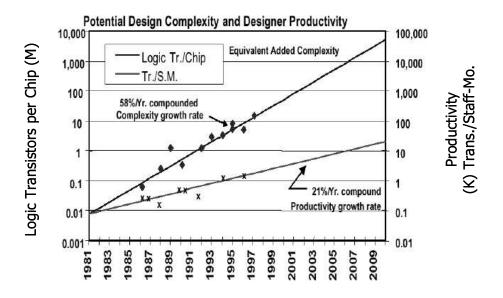

With the semiconductor processing technology entering in the deep sub-micron era, it has long been recognized that the gap between the processing capability and design capability is not decreasing but increasing, which is known as the design productivity gap. As illustrated in Figure 1.1, the design productivity (number of transistors designed by a designer in one month) increases only 21% a year, whereas the design complexity (number of transistors in a typical design) increases 58% a year. The bottleneck here is not only what we can produce now, but also what we can design. A direct result is the number of designer months (number of designers times total time) in a design project is increasing rapidly. The design cost has become the greatest threat to the continuation of the semiconductor roadmap.

The second problem the designers will confront is the extremely high manufacturing nonrecurring engineering (NRE) cost. As the semiconductor industry approaches the 100-nm technology node, the NRE (mask set and probe card) costs are getting close to \$1 million for a large integrated circuit (IC). With an average of just 500 wafers produced from each mask set, rapid growth of manufacturing NRE can throttle the initiation of new IC design projects.

The answers to the design productivity gap problem can come from a) novel system-level design specification; b) hardware-software codesign; and c) substantially reuse intellectual property (IP) components [17]. This caused the revolution of System-on-Chip (SoC) design. To solve the problem of the manufacturing NRE cost, we have to produce the same IC in very high volume to reduce the average NRE cost on every chip. This leads us to the motiva-

Figure 1.1: Design productivity gap (source: ITRS'99).

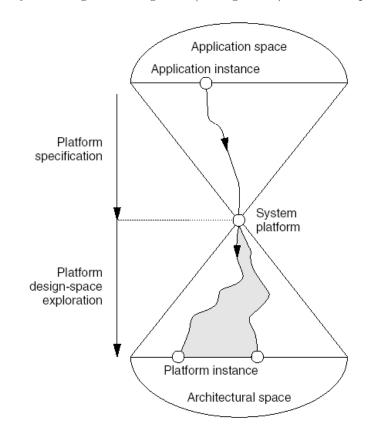

tion for a move to platform-based-design (PBD) [108, 37]. The emerging of SoC and PBD has also moved the design complexity from the hardware side to the embedded software side, which is increasing amazingly at a speed of 140% per year and will account for more than 80% of the total design cost according to the ITRS 2003 roadmap in the near future. All these require a novel system-level design methodology for the embedded software, especially to manage the concurrent tasks running on a SoC. As Jan Rabaey said in his keynote speech in DesignCon'04 [131], "It's easy to create concurrency [by putting several components/processors on the same chip], but it's difficult to manage concurrency."

#### 1.1.1 The System-on-Chip Era

The complexity of systems is surging due to the exponentially increasing transistor count enabled by smaller feature sizes and spurred by consumer demands for increasing functionality, lower cost, and shorter time-to-market. To design such complex systems, tradeoffs must be made between all aspects of value or quality, and all aspects of cost.

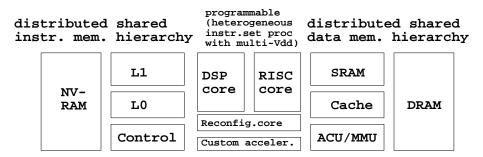

An SoC is a complex IC that integrates the major functional elements of a complete end-product into a single chip or chipset [108]. In general, SoC design incorporates one or more programmable processor cores (homogeneously or heterogeneously, even reconfigurable), on-chip memory, and accelerating function units implemented in hardware. It also interfaces to peripheral devices and/or the real world. SoC designs encompass both hardware and software components. Because SoC designs can interface to the real world, they often incorporate analogue components, and can, in the future, also include opto/microelectronic mechanical system components. These components are connected with one or more links, either bus, crossbar, or network-on-chip. Figure 1.2 shows an example of such a device.

Figure 1.2: A typical System-on-Chip device.

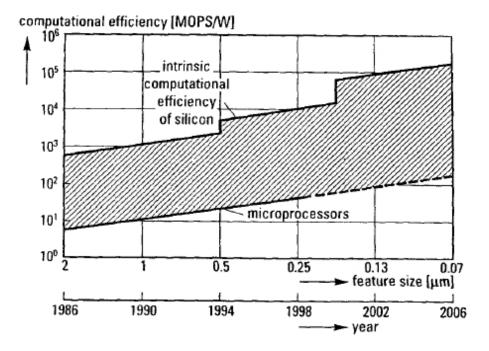

One issue that is worth noting is the trend of putting more than one processing elements into SoCs, either heterogeneously or homogeneously. Adding reconfigurable processing units is also an option. This can be explained by the daunting challenge of managing the SoC power, especially for low-power, wireless, multimedia applications, which needs application-, OS- and architecture-level optimizations including parallelism, and adaptive voltage and frequency scaling. The upper curve of Figure 1.3 gives the intrinsic computation efficiency available from silicon, while the lower one shows the computation efficiency of a single traditional, instruction based processor. From that figure, it is clear that traditional single processor solution is becoming extremely inefficient. An example is the Pentium from Intel. While we are passing 3GHz CPU frequency, it consumes more than 100W and is definitely not the solution to embedded and portable devices, which require processing performance around 2GOPS (Giga Operations Per Second) at average power consumption as low as 0.1W (ITRS 2003 roadmap). However, if we put 4 Pentium cores on an SoC, to provide the same computation power, each core has only to work at one forth of the original frequency. Hence the total power consumption can be reduced dramatically (theoretically the power is reduced by 64 times and the energy is reduced by 16 times, as explained later, if full voltage scaling is allowed<sup>1</sup>). Dif-

<sup>&</sup>lt;sup>1</sup>In reality, the possible  $V_{dd}$  variation is limited by the processing technology. However, techniques such as multi- $V_t$ , multi- $T_{ox}$ , multi- $V_{dd}$  can be applied simultaneous in a single core

Figure 1.3: Computation efficiency vs. minimum feature length and time [30]. MOPS is Million Operations per Second.

ferent kinds of processors (microprocessor, DSP, ASIP, ...) have different kinds of application domain and different performance/power ratio. For example, for signal processing, a DSP is more efficient with respect to power dissipation and chip area, while a microprocessor is more efficient in handling control-flow specific code. It is possible to explore different levels of parallelism intrinsic in an application and to distribute them to different (kinds of) processors so that the highest power efficiency is achieved. That explains the move to heterogeneous multiprocessor platforms.

The required shift for SoC design is the result of two industrial trends: the development of application-oriented IC integration platforms for rapid design of SoC devices and derivatives, and the wide availability of reusable virtual components [24]. The most obvious way to combine flexibility and cost efficiency is to take the best from both. By their nature, software implementations on programmable cores are preferred to realize maximum flexibility. Tasks which run inefficiently in software, have to be mapped on co-processors (or specific pro-

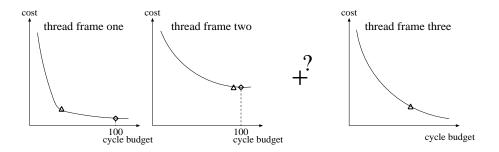

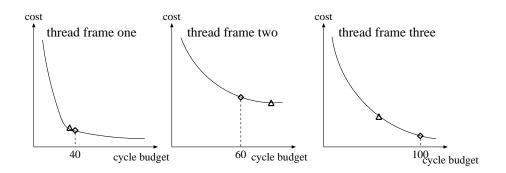

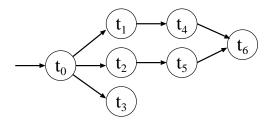

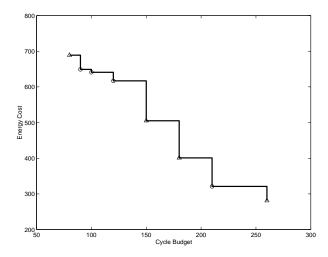

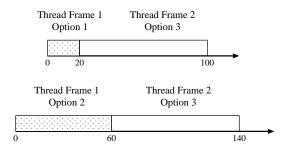

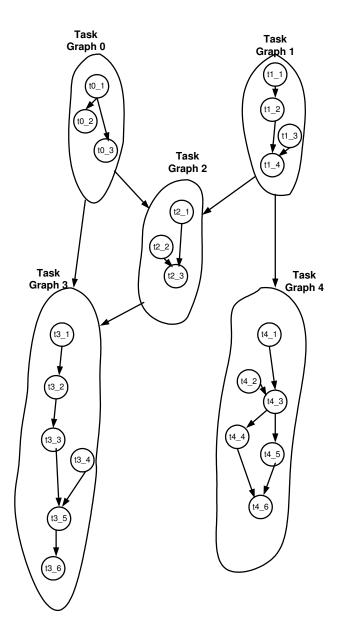

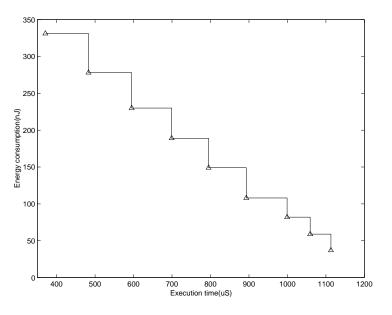

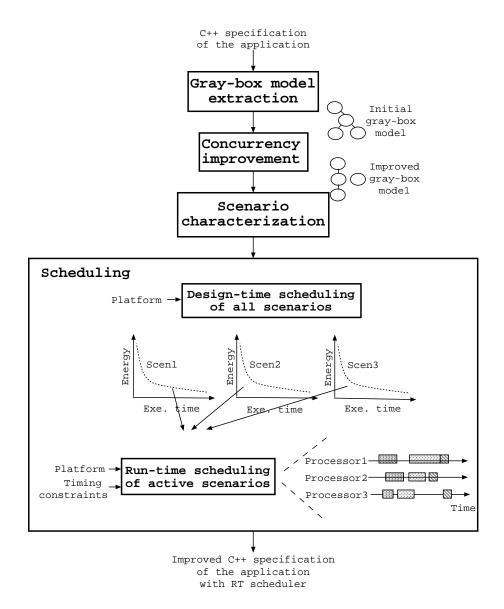

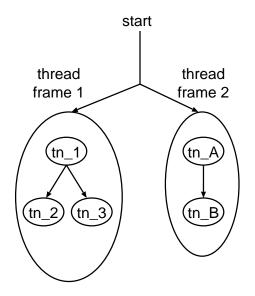

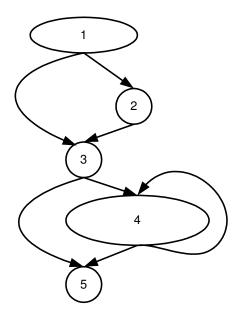

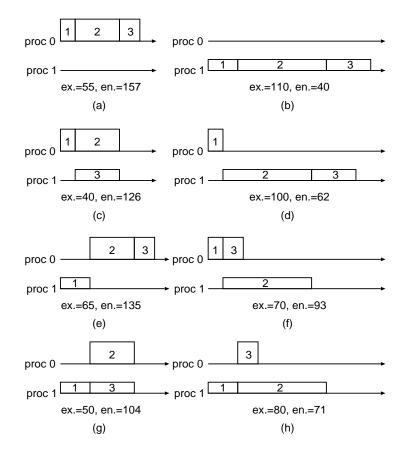

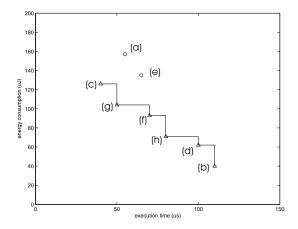

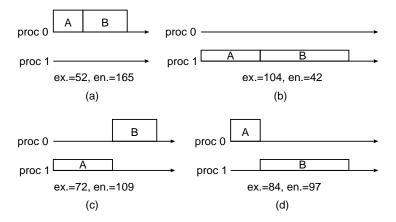

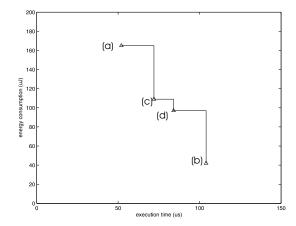

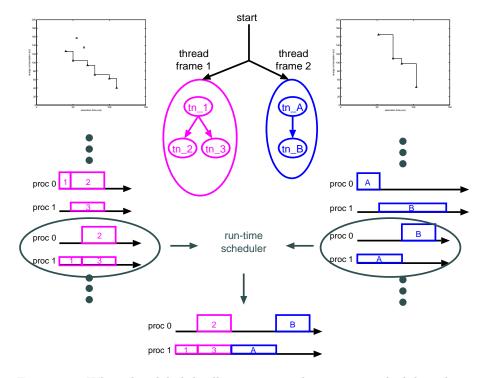

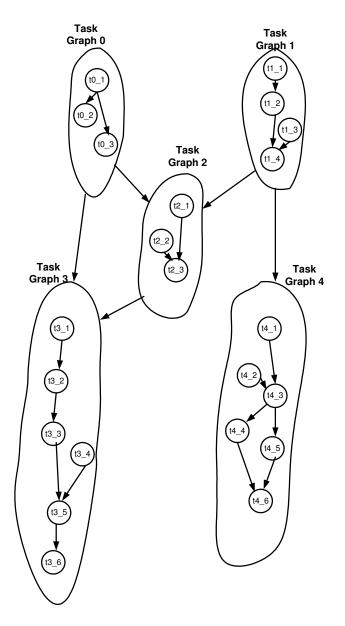

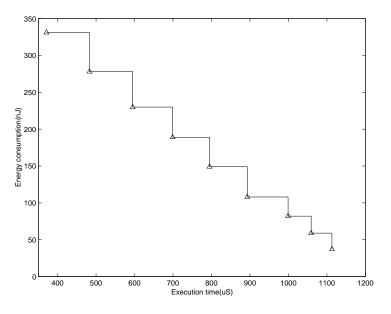

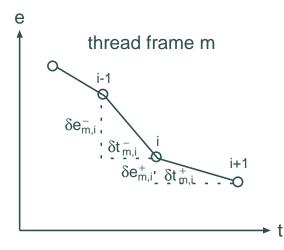

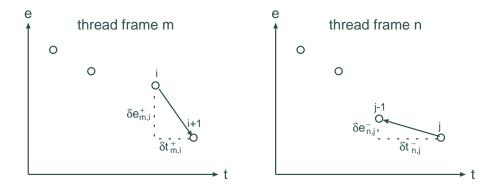

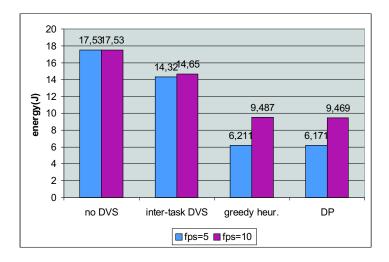

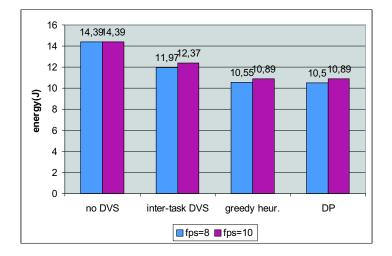

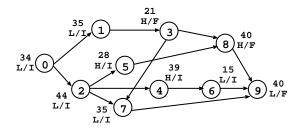

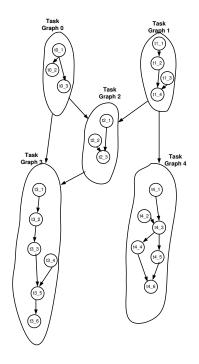

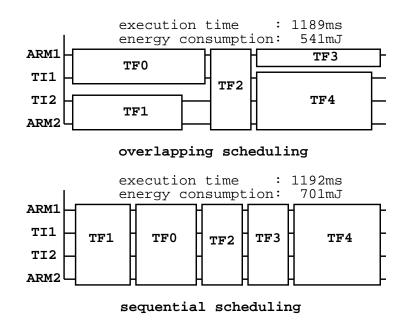

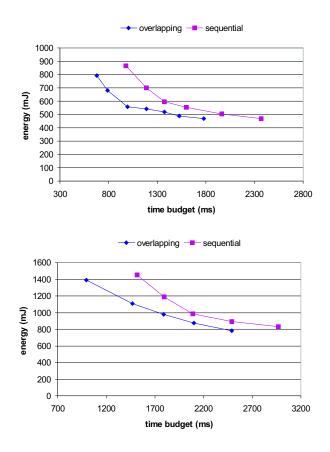

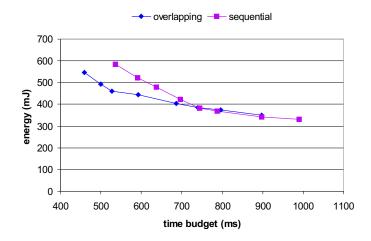

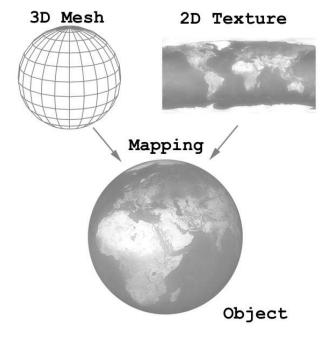

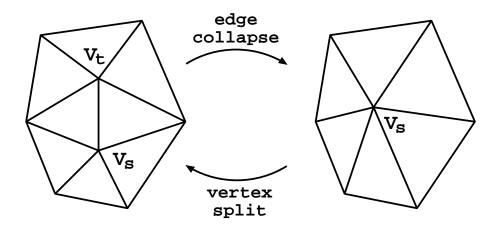

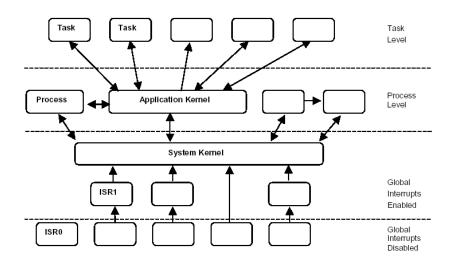

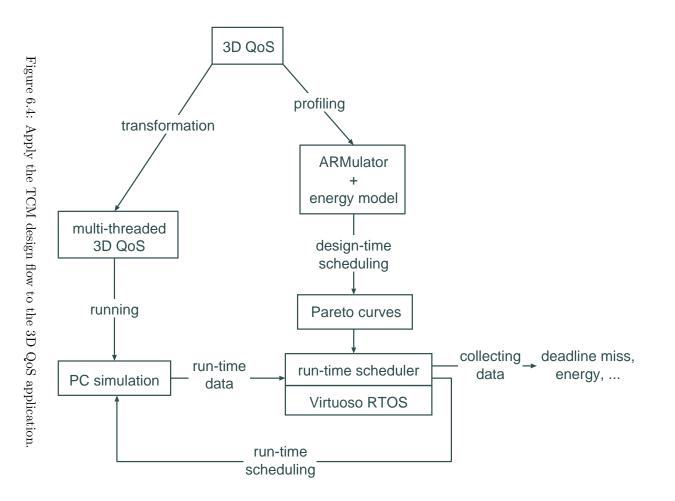

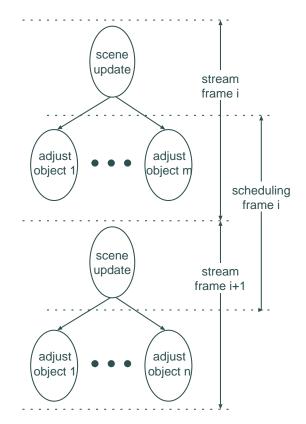

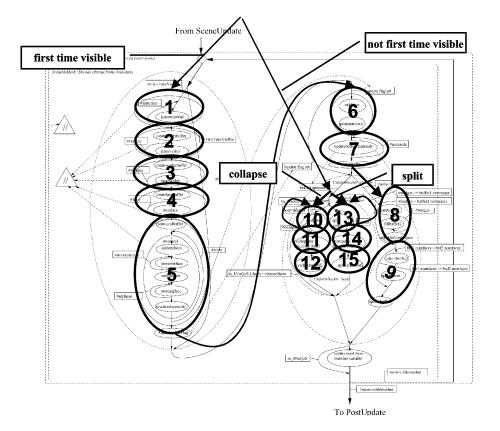

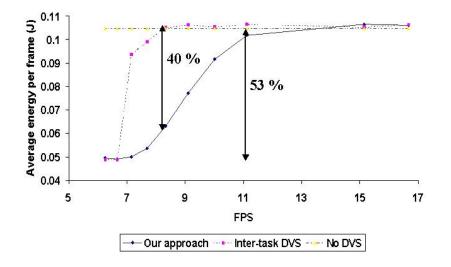

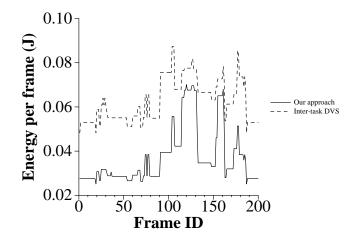

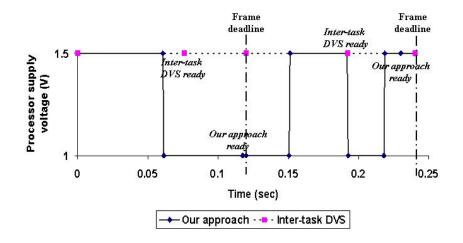

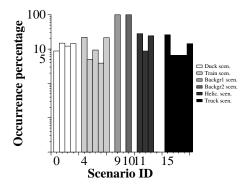

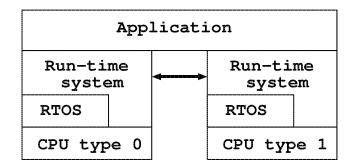

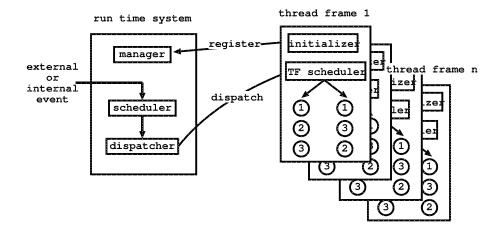

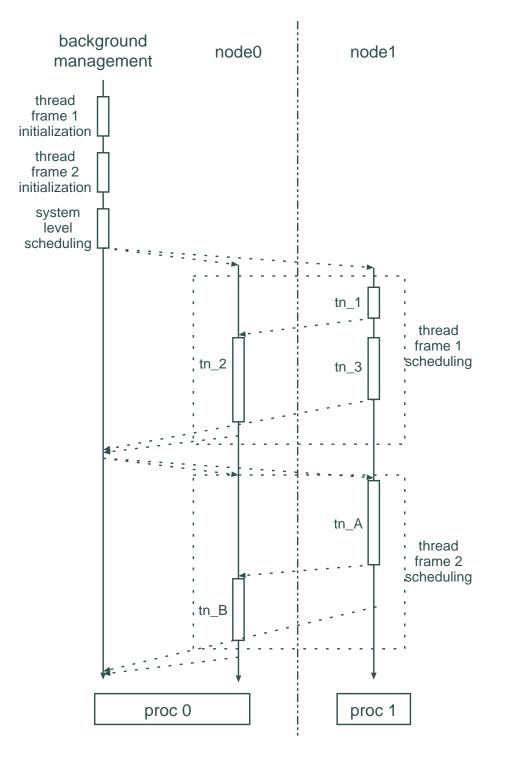

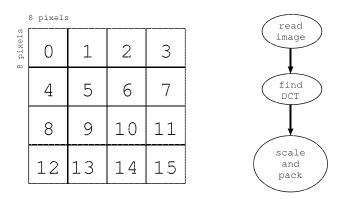

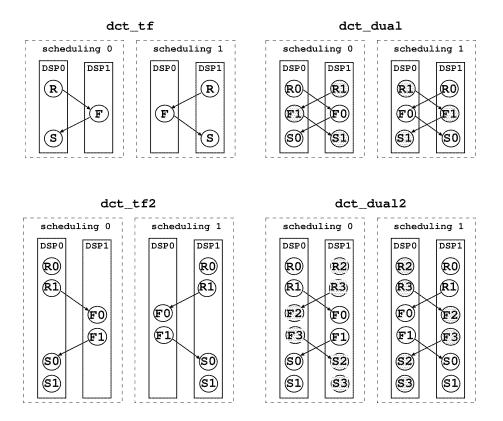

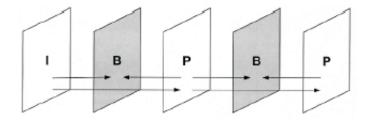

to achieve ultra low power/energy consumption at a reduced performance level. Multi- $V_t$  and multi- $T_{ox}$  are mainly useful for reducing the static leakage power.