# **INFORMATION SOCIETY TECHNOLOGIES**

# (IST)

# PROGRAMME

Contract for: Shared-cost RTD

Annex 1 - "Description of Work"

Project acronym: POET

Project full title: Power Optimisation of Embedded SysTems

Contract no.:

Related to other Contract no.:

Date of preparation of Annex

Proposal number: IST-2000-30125

Operative commencement date of contract:

| 1. Pi  | roject Summary                              | 4 |

|--------|---------------------------------------------|---|

| 1.1.   | Objectives                                  | 4 |

| 1.2.   | Description of Work                         | 4 |

| 1.3.   | Milestones and expected Results             | 4 |

| 2. Pi  | roject Objectives                           | 5 |

| 2.1.   | Main Objectives                             | 5 |

| 2.2.   | Objectives per Partner                      | 6 |

| 2.3.   | Results                                     | 7 |

| 3. Pa  | articipant list                             | 7 |

| 4. C   | ontribution to Programme/Key Action         | 8 |

| 5. In  | novation                                    | 9 |

| 5.1.   | Design Flow1                                | 0 |

| 5.2.   | State of the Art: Design Tools1             | 1 |

| 5.3.   | Target Applications1                        | 3 |

|        | ommunity added value and contribution to EU | ~ |

| polici | es13                                        | 3 |

| 7. C   | ontribution to Community social objectives1 | 5 |

| 8. E   | conomic development and S&T prospects       | 6 |

| 8.1.   | Market Position1                            | 6 |

| 8.2.   | Consortium Exploitation plan2               | 1 |

| 8.3.   | Individual Exploitation plans2              | 2 |

| 9. W   | orkplan2                                    | 5 |

| 9.1.   | General Description2                        | 5 |

| 9.2.  | Workpackage List                              | 28 |

|-------|-----------------------------------------------|----|

| 9.3.  | Workpackage Descriptions                      | 29 |

| 9.4.  | Effort Overview                               | 49 |

| 9.5.  | List of Results                               | 49 |

| 9.6.  | List of Deliverables                          | 50 |

| 9.7.  | Project Planning and Timetable                | 52 |

| 9.8.  | Graphical Presentation of Projects Components | 53 |

| 9.9.  | Project Management                            | 54 |

| 10.   | Clustering                                    | 55 |

| 11.   | Other contractual conditions                  | 56 |

| Apper | ndix A : Consortium Description               | 57 |

| A.1 I | Kuratorium OFFIS e.V. (OFFIS), Germany        | 57 |

| A.2 ( | CEFRIEL, Italy                                | 58 |

| A.3 I | Politecnico di Torino (POLITO), Italy         | 59 |

| A.4 / | Alcatel SEL (ASEL), Germany                   | 60 |

| A.5 / | ARM Limited (ARM), U.K                        | 60 |

| A.6 ( | DSC, Germany                                  | 61 |

| Apper | ndix B : Contract Preparation Forms           | 63 |

# 1. Project Summary

# 1.1. Objectives

The main objective of the POET project is to develop a new design methodology and tool suite for power estimation and optimisation in heterogeneous embedded SoC designs. The key innovation of the approach is to enable design space exploration for low power system architectures, algorithm optimisations and system partitioning - from the earliest design steps seamlessly through to RT level (i.e. to the interface with standard industrial synthesis tools). The POET design framework will operate at each level of abstraction, i.e. algorithmic, hardware/software partition, cycle-accurate RT level. POET tools will manage and optimise all major contributors to power dissipation in large SoC designs such as ASICs, cores and processors, memories, communication and I/O interfaces.

# 1.2. Description of Work

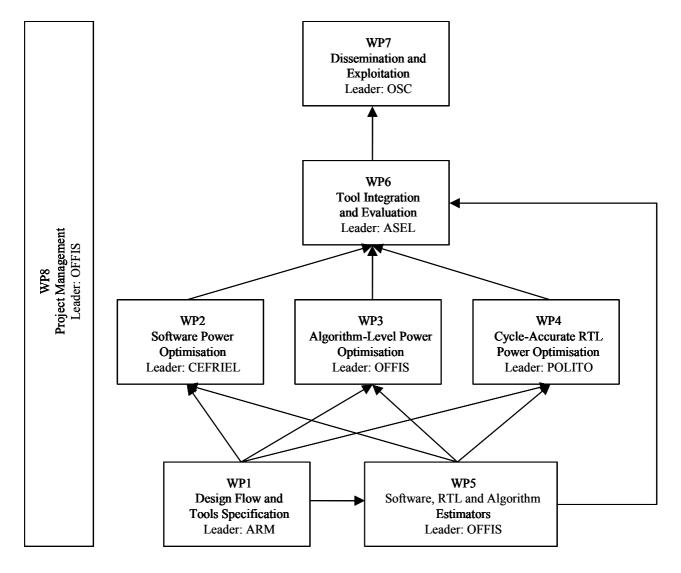

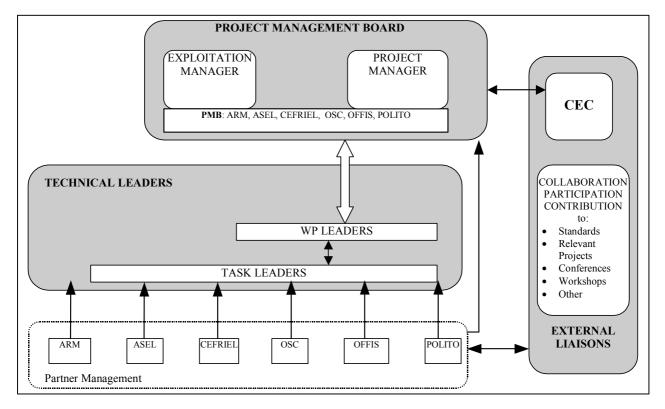

The workplan is structured into eight workpackages (WP): six technical(WP1-6), one commercial(WP7), and one administrative(WP8). WP1 specifies the design flow for the development of low power integrated SoCs, defining the interfaces between the different power optimisation tools so they are able to interact seamlessly. WP2 develops methodologies to optimise power consumption of the software components of SoC design -based on the power estimation techniques previously developed and enhanced in WP5. The SoC design outcome will be dependent on the architecture adopted in terms of processor and memory hierarchy, and on the compilation and operating system environment. WP3 deals with the development of methodologies and develops a prototype tool for interconnect and data manipulation. WP3 also develops the transfer and storage driven power optimisation of executable specifications of hardware units, including memory structures; these will be implemented using SystemC and C++. WP4 deals with the development of methodologies and prototype tools for power optimisation of memory sub-systems, and of the memoryprocessor and data-path communication interfaces. This enables automatic insertion of power management circuitry in cycle-accurate RT level descriptions, and automated synthesis of power managed RT level library macros. WP5 enhances the capabilities of power estimation tools already developed by Partners 1, 2 and 3 (partly in a previous ESPRIT project) so that the tools can interact fully with the new optimisation tools developed in WP2, WP3 and WP4. WP6 deals with the integration of the tools developed in POET, and with industrial evaluation of the tools in the application domains of the user partners. WP7 deals with both internal and external exploitation and commercialisation. WP8 deals with project co-ordination and management of POET, including financial and contractual administration.

# 1.3. Milestones and expected Results

Key milestones and results:

the preliminary and final versions of the different estimators and optimisers integration of the POET tool chain industrial evaluation of the tools implementation of the exploitation plan

# 2. Project Objectives

The overall objective of the POET project is to address an increasingly limiting factor in system-level design – the control and design management of power consumption at all stages of the design process. Achieving integrated power management at the design-in level is becoming a key requirement for advanced silicon systems, and is increasingly necessary to enhance the competitiveness of the European silicon, communication and information processing industries.

Europe has strong and recognised capabilities in advanced SoC (Systems-on-Chip) design. As power management becomes *the* decisive factor in aspects of new ASIC design for certain new classes of products, especially small embedded and portable systems, it is becoming essential that European industry be able to mobilise new tools and methodology and compete with the best in the market. It is widely recognised that the leading EDA tools (Electronic Design Automation) mostly originate in the USA: the POET project intends to develop its tools and methodologies so they can be directly coupled with leading commercial EDA systems. This will enable us to develop and strengthen the excellent position of Europe in the area of system-level design tools, itself an emerging market where European companies have excellent opportunities. In turn, this will have a direct impact on European essential technologies and infrastructures for mobile communication and ubiquitous computing, as well as in the integration of both into integrated systems and services.

Current integrated digital Systems on Chip (SoC) designs pose new challenges to the development of a consistent and seamless design flow. The heterogeneous nature of various components of such systems (memories, IP programmable and non-programmable cores, glue logic) requires new design tools both for analysis and for optimisation. In particular, many of these systems find their application in the mobile domain, such as cellular phones, personal digital assistants and wireless Internet terminals. Therefore, there is an increasing demand from both semiconductor manufacturers and system houses for EDA tools that can help in addressing the power consumption problem during product development. Whilst significant research effort has been made in the recent past for studying and prototyping new computeraided design solutions - both for power estimation and optimisation - the scenario of commercially available tools is still relatively poor. This is especially true at the highest levels of design abstraction, i.e. RTL (Register Transfer Level) and algorithm levels. In addition to hardware optimisation, embedded software design and instruction-level optimisation is quickly becoming more relevant. In the main, this is due to the co-design approach for many new designs coupled with the rapidly increasing presence of re-used and re-usable computational units and other logic blocks (e.g. CPU cores, DSPs, I/O and other micro-controllers) in contemporary digital applications.

The overall objective of the POET project is to address an increasingly limiting factor in system-level design – the control and design management of power consumption at all stages of the design process. Achieving integrated power management at the design-in level is becoming a key requirement for advanced silicon systems, and is increasingly necessary to enhance the competitiveness of the European silicon, communication and information processing industries.

# 2.1. Main Objectives

Power dissipation is increasingly becoming a limiting factor in the integration of complex SoC (System-on-Chip) designs. This is starting to impact the mobility of ubiquitous computation and communication, as well as affecting the cost and reliability of communication systems and networks. Power management and reduction is most efficiently achieved at the system level, at the stage when algorithms are developed and partitioning is done. Experiments have shown that at one extreme, power reduction of several orders of magnitude can be achieved

between the best combination of algorithms and architecture versus non-optimised solutions. The POET project addresses this opportunity as its main objective – the development and integration of methodologies and tools for power estimation and optimisation of combined SW and HW descriptions of SoC systems. POET targets the algorithmic level for both hardware and software as well as the functional RT level of abstraction where power optimisations can offer the largest potential.

The various tools to be developed will operate at different levels of abstraction (including application-level software, algorithmic, cycle-accurate RTL) and will address all major contributors to power dissipation – especially in large SoC implementations. Since software and algorithm development of SoCs is mostly done in the C programming language, C will be directly supported as an input language for the system specification. The RT-level optimisation and interface to the back-end design flow will be based on VHDL so that it is consistent and compatible with the established silicon manufacturing design flow. In order to achieve these objectives, the following key activities will be addressed by the POET project: Build and demonstrate a complete working design flow for power optimised SoCs from system specification to the RT synthesis level, showing significant reduction in overall design time and power reduction, with minimal overhead in terms of performance and silicon real estate. Implementation of the design methodology in an efficient and integrated tool set, where not

available commercially, in particular:

A prototype tool for power optimisation of C code specific to dedicated target platforms A prototype tool for low power high level synthesis of designs with C-based specifications. A prototype tool for power optimisation at the RT level of abstraction.

Evaluation and qualification of the project's results.

Augmentation of CAD product suites with innovative power design management software.

POET will also further develop and enhance the power analysis and estimation tools already developed by partners within a previous ESPRIT project. This will adapt them to the needs of an *integrated* environment required for advanced SoC designs, where estimation and optimisation must be carried out in an interleaved fashion throughout the design process.

# 2.2. Objectives per Partner

The relevance of the POET project also has direct commercial advantage to the project's participants:

OFFIS is extending its position in the high-level power estimation and optimisation domain.

CEFRIEL is consolidating its competence in power estimation and optimisation technology for embedded software.

POLITO is strengthening its position in the low power scientific community with particular focus on RT-Level estimation and optimisation.

ASEL gains commercial advantage by having access to the most advanced tools and methodologies for power optimisation of network switching and access systems, especially in customer premises and central office equipment in the ADSL and HFC (hybrid fibre coax) domain.

ARM is strengthening and consolidating its world-leading position in low power embedded cores by offering its customers a seamless tool flow for power optimised embedded software and core based architectures for embedded SoC designs.

OSC is extending its position in the European EDA market by offering advanced and integrated tools for the growing low power market.

# 2.3. Results

The principal results of the project will be:

Enhancement of various existing EDA tools and prototypes for hardware and software power **estimation** of embedded SoCs, usable at various stages of the design flow. New EDA tools for hardware and software power **optimisation** of embedded SoCs. Improved design capabilities of the user partners (ASEL and ARM). Power optimised designs of the user partners, with attendant commercial advantage. Dissemination of innovative research results within the community of IC and system designers.

# 3. Participant list

| Participant<br>Role | Participant<br>Number | Participant<br>Name      | Participant<br>Short Name | Country           | Date enter<br>Project | Date exit<br>Project |

|---------------------|-----------------------|--------------------------|---------------------------|-------------------|-----------------------|----------------------|

| С                   | 1                     | Kuratorium<br>OFFIS e.V. | OFFIS                     | Germany           | Start of<br>Project   | End of<br>Project    |

| Р                   | 2                     | CEFRIEL                  | CEFRIEL                   | Italy             | Start of<br>Project   | End of<br>Project    |

| Р                   | 3                     | Politecnico<br>di Torino | POLITO                    | Italy             | Start of<br>Project   | End of<br>Project    |

| Р                   | 4                     | Alcatel                  | ASEL                      | Germany           | Start of<br>Project   | End of<br>Project    |

| Р                   | 5                     | ARM                      | ARM                       | United<br>Kingdom | Start of<br>Project   | End of<br>Project    |

| Р                   | 6                     | OSC GmbH                 | OSC                       | Germany           | Start of<br>Project   | End of<br>Project    |

# 4. Contribution to Programme/Key Action

This proposal addresses Key Action IV, *Essential Technologies and Infrastructures*, Action Line 8, *Microelectronics – optoelectronics*, Task 8.1: *Microelectronics Design and Test*, Focus (ii) *Low Power design.* The proposal also contributes to Key Action IV, Action Line 8, Task 8.2: *Application-specific microelectronics* by addressing tools and methods for embedded software especially towards low-power.

The main objective of Key Action IV is to accelerate the take-up of technologies vital for the Information Society, and to broaden and deepen their field of application. As these general objectives state, some of the most promising but also most challenging opportunities are in the common usage of infrastructures for multiple applications, e.g. communication and its infrastructure, mobile information retrieval and ubiquitous computing. The POET proposal will enable design technologies particularly for power-sensitive mobile terminals and network infrastructure.

The POET project will contribute to the goals of the program by developing a tool-suite for fast, yet accurate power estimation and **optimisation** of designs, starting from high level abstraction down to the functional RT level. As power consumption is becoming a critical issue in the development of many digital systems, tools that allow designers to control and optimise the power budget during the various phases of the development process are in increasing demand. From an initial, system-level specification of the design, several

partitioning/synthesis/estimation/optimisation steps are required to deliver a power-efficient architecture capable of meeting all the constraints posed at the specification stage. The required computational complexity for future mobile applications is increasing faster than the expected growth in DSP processing power (as predictable by Moore's Law). Consequently, combined HW/SW SoC designs will be needed to implement this class of systems. Also, it is clear that this computation power will then consume more electrical power. Without considerable improvements in power-optimised design techniques, the increase in power may be much larger than the predicted increase in battery capacity ('Ever-Ready' Law) and the natural reduction in power consumption resulting from smaller geometries and lower operating voltages.

Within this application area (and especially in 2G mobile phones) European suppliers hold a substantial share of the total world market. This is due in part to the advanced technological lead and know-how of the European industry in this domain. The ability to efficiently design microelectronic components with low power consumption is one of the most important enabling technologies for success in the fastest growing markets, such as integrated mobile computation and communication, and consumer equipment such as MP3 Players, PDAs and mobile phones. From a simplified viewpoint, the strong position of the communication industry in Europe is in contradiction to the small EDA industry in Europe. However, many of the more innovative EDA solutions – in particular for signal processing, HW/SW co-design, mixed-signal, and safety critical system design – have their origins in Europe due to the innovative strength of the European research community. Many tools have been developed in Europe, driven by industrial needs – in some cases partly with EU-funding. These have been productised by start-ups and brought to market either directly or through trade acquisition. The benefit to the system industry remains – access to tools which address European system design house needs.

POET's approach of power management designed-in rather than grafted on afterwards in expensive rework directly addresses the problem described in the 1999 Int. SIA Technology Roadmap: "Better methods of accurate power prediction and analysis are more important than ever. Power prediction must be done as early and as accurately as possible in the design cycle, if possible at the architectural design phase. More and more applications have power budgets that cannot be exceeded for one reason or another, usually portability or reliability for a given package or system. Inaccurate power estimates often result in rework of the design architecture, logic, timing or sometimes costly rework of an analogue block, and results in delays in the design and lost market opportunity."

# 5. Innovation

Modern integrated digital systems are characterised by complex and heterogeneous architectures, posing several new challenges to design flow development. The main challenge consists in the very diverse nature of the various elements of a system. Most digital Systems-on-Chip (SoCs) contain:

More than one, often several large-scale intellectual property (IP) cores such as dataprocessors (RISC cores, DSP data-parallel processors, dedicated functional units), microcontrollers, peripherals (PCI interfaces, serial and parallel drivers, external DRAM controllers, JTAG controllers, etc.)

A significant amount of memory in various forms and granularity levels, such as large DRAM banks, fast SRAM buffers, caches and register files, FLASH memories for non-volatile storage Synthesised logic for interfacing large IP components and for supporting critical application-specific functionalities for which IP cores are either not available or inefficient Other blocks, such as analogue components, sensors, and actuators, often operating in a mixed-signal domain

This heterogeneity shifts the design paradigm from classical "synthesis" to the most abstract task of *integration*. The use – and the relative assembly – of several pre-designed and pre-verified components (e.g. memories, and the IP blocks) is generally a more difficult, and less automatable, task than the translation of a consistent high-level description into a lower-level one, such as conventional RTL synthesis. For instance, the push for maximum reuse of IP components increases the importance of the optimisation potential contained in the *interfaces* between blocks, as well as that contained in their behaviour, as in the conventional approach. Classical hardware optimisation techniques are still important for the glue logic, needed for the interfaces between such blocks. Moreover, software is now a primary component of such systems, and the impact of software operations on the hardware can no longer be disregarded.

Computer-aided design frameworks developed in the past have focused on more homogeneous and conventional architectures, but the increasing need for design aids for heterogeneous SoCs prompts for a new generation of tightly integrated tools. These tools can help designers to both validate and optimise complex integrated systems, typically containing a large amount of memory, several IP cores and custom-synthesised application-specific logic.

Validation and optimisation of large systems on silicon have been studied extensively by the research community. The common approach taken in the past was to raise the abstraction level, in order to tackle system-level design issues as early as possible, usually in the initial phases of the design process and possibly even when functionality is still being specified together with design constraints. This approach has several advantages, but in particular it helps designers adopt a robust, top-down methodology, and to avoid major pitfalls early in the design process.

The output of system-level design tools is a partitioned specification, where part of the system functionality is implemented in software – to be executed by one or more processing elements – and part is assigned to dedicated hardware. Usually, software components are output in a high-level programming language (C, C++, Java, etc.), whilst hardware components are specified in a HDL (Verilog, VHDL). The common assumption is that the software and hardware components are processed separately by back-end tools, and only towards the end of the process are the end results of the software synthesis flow and the hardware synthesis flow merged and fed to a co-simulation engine for functional validation.

The main limitation of this approach is that it does not account for the complex (and often poorly understood) interdependencies between the different types of components in

heterogeneous hardware architectures early in the design flow. For instance, when synthesising software we need to avoid neglecting the requirements that the software execution imposes on the on-chip memory system and on the peripherals for off-chip memory access (for example, the allocation of data structures with respect to the memory architecture). Similarly, hardware specification and synthesis are heavily impacted by interfacing issues when the software is running on the core processors (for example, the locality of memory accesses). In general, it is not sensible to neglect the obvious fact that hardware and software interact directly, and that they compete for shares of a common power budget and limited silicon area. The interaction between system components has been a central issue in several recent initiatives in system level design. Design targets in performance, silicon area and power can be met only if a comprehensive view of the entire system is maintained – particularly as the design is processed from the system level down to lower abstraction levels.

This basic observation is at the foundation of the POET research effort. Our primary focus is on power consumption, its estimation and optimisation in large, heterogeneous SoCs. For this purpose, we plan to exploit some research effort developed in a previous ESPRIT project, that can be considered as the infrastructure for the proposed design methodology. In particular, we will re-use the technology provided by a set of power estimation tools applicable at different levels of design abstraction (namely, software, algorithmic and RTL), that should be used as analysis tools in the POET project.

The POET project is conceived with a three-fold objective: First, to enhance the available analysis and estimation tools, by adapting them to the needs of an integrated environment such as that of SoCs, where estimation and optimisation must carried out in an interleaved fashion. Secondly, to build a set of power optimisation methodologies and tools for heterogeneous SoCs. This objective represents the biggest challenge, because a suite of power optimisation nor consider a single contributor to the overall system power. Thirdly, to develop a low power system level design flow and to demonstrate the applicability, efficiency and quality of the tools on concrete industrial design cases from leading system houses and on most common platforms.

## 5.1. Design Flow

Currently low power design in practise means: low voltage, small feature size, clock gating, operand isolation, and power management. Clearly low voltage is a key influence on power reduction due to its quadratic impact on the power dissipation. However, there are limits due to reduced performance and increased leakage current. Further small feature size reduces the switched capacitance and hence significantly reduces power. Usually these parameters are not at the distinction of the designer and their positive effect are assumed in the power dissipation predictions of the roadmaps anyway. Other means at the gate and circuit level provide only power reductions in the area of some 10-20%.

Power estimation and optimisation at the system level, during software design and system architecture definition, have been addressed by prior research work. However, no seamless design flow approach through these levels - considering the main power drains - has been developed and applied so far. Within POET this flow will be defined driven by concrete product developments by the user partners ASEL and ARM. The flow will be coupled to industry standard commercial tools as far as available, and missing links in the tool chain will be developed by the research partners of the project (OFFIS, CEFRIEL and POLITO) and commercially made available by the EDA partner OSC.

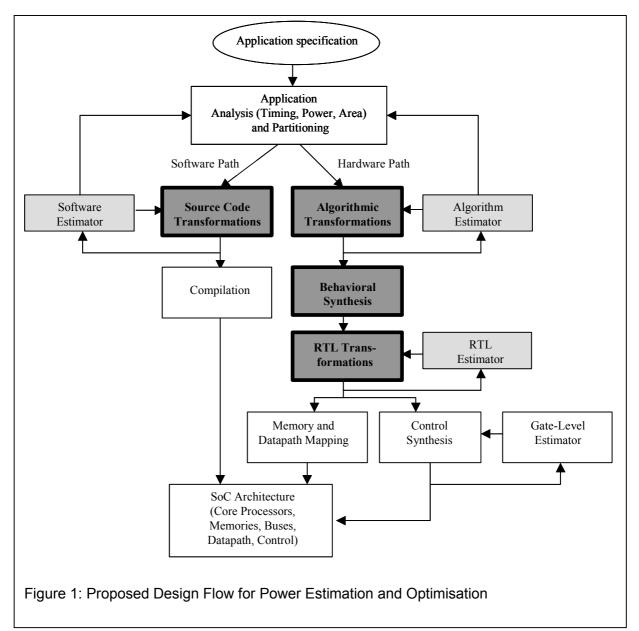

For proper power analysis and optimisation, a full characterisation of the system components is needed. In order to minimise the time-consuming characterisation procedure, the number of libraries and technology files will be kept at a minimum. Figure 1 shows a preliminary design flow for power optimisation. dark grey boxes denote new developments in POET whilst light grey indicates parts of the design flow which already exist in prototype form and will be enhanced in POET to fully support the optimisation phases.

# 5.2. State of the Art: Design Tools

At the current time, there are no commercially available tools in existence which provide a comprehensive, integrated, multi-level design methodology for heterogeneous architectures.

There are a few stand-alone tools – mainly in the form of academic prototypes – that do exist, most of which target optimisation at a single, specific point in the design flow, as detailed later in this section.

Tools developed and integrated in the POET project will span several levels of abstraction and tackle all major contributors to power dissipation in large systems on silicon. To support this view, a power optimisation methodology is planned which spans three abstraction levels: *Software, algorithmic* and *cycle-accurate RTL*.

The <u>software level</u> concerns the software functions which run on the core/DSP processors. The output of POET will be the identification of design guidelines (at source level), tailored to reduce power requirements. Where practical, software transformations will be identified, which can be semi-automatically applied to existing application software at different levels of abstraction and stages of the synthesis flow. Prior the identification of the design strategy, an extensive analysis of the impact on power consumption of typical basic C-constructs and design templates will be carried out. In particular, the influence of data types, classes of operations and control structures on the overall power budget will be analysed. Other effects will be taken into account, such as the cross-interaction between the above basic elements, the presence of procedure calls and the use of dynamic memory. A suitable set of models and estimators will be identified to characterise the different aspects which influence code execution and related energy dissipation, including microprocessor-related power consumption of compiled code, data caching and data transfer, and application profiling. The methodology will be developed and tuned by consideration of a relevant set of real-world benchmark applications, to identify the typical kernels and software templates.

The <u>algorithmic level</u> refers to a functionally accurate algorithmic specification of the system. At this level of abstraction, the correspondence between operations and their execution time is not fully specified. Throughput, latency and synchronisation constraints are specified, however, and must therefore be taken into account during optimisation. The algorithmic specification can either be implemented in software, executing on a programmable processor, or be mapped onto dedicated hardware to be synthesised in later design steps. The decision on hardware-software partition is either left to the designer or to a higher-level design tool. It is assumed that the algorithmic specification contains specific annotations which specify the target mapping (hardware or software).

The <u>cycle-accurate RTL</u> refers to the conventional hardware description style used by designers in the synthesis domain. The main difference in terms of semantics – with respect to algorithmic descriptions – lies in the explicit notion of time that is assumed throughout the description. Operations happen between clock cycles, representing the smallest possible granularity. Another significant difference is represented by the type of simulation each description style can support – behavioural descriptions are purely functional (and therefore very fast), whereas cycle-accurate simulation requires synchronisation with a periodic time reference which determines the length of the simulation cycles. This cycle-accurate RTL differs from *structural* RTL, where the binding of synthetic operators to specific RTL library modules, such as adders and registers, is explicitly specified by means of the interconnection of the various blocks.

Two of the three main development activities in POET, carried out by CEFRIEL and OFFIS respectively, focus on algorithmic optimisations for software and for hardware. The third main development activity, lead by POLITO, targets the optimisation of power dissipation starting from a cycle-accurate specification. Algorithmic and cycle-accurate optimisations are intended to be carried in sequence, i.e. the former provides the input to the latter. It is important to emphasise that this two-phase optimisation approach does not take a partial view of the overall system power, but moves from a comprehensive view of all major contributors to the power budget. Approaches which do not account for all of these components may succeed only in reducing energy consumed in *part* of the system, which may only have a marginal impact on overall system power. More problematically, they may even increase overall power consumption by causing uncontrolled increase of power consumption in parts of the system

outside the optimisation scope (but which are tightly connected to the initial optimisation target).

# 5.3. Target Applications

The ASIC department of the Switching & Routing systems division of ASEL is working in the area of very advanced, high complexity ASICs on a large variety of telecommunication areas. This includes not only ASIC designs for ISDN and ATM switching products or cross-connect transmission systems, but also ASICs for access systems that are located at the central office or in customer premises equipment. In addition, the ASIC department has built up core competence knowledge in the area of embedded systems design and provides a configurable embedded processor platform to other ASIC design centres in terms of an intellectual property. This includes not only the VHDL and embedded software code, but also the provision of a methodology for using the processor platform within other designs, i.e. a compilation, synthesis, co-simulation, verification and test strategy. ASEL is in charge of extending its processor platform methodology to cover also low power design issues and tools, as low power is and becomes a crucial matter for ASIC designs throughout ASEL. ASEL especially sees the need for power estimation and optimisation tools that can be used very early in the design phase and that covers also the proportion of the power that is consumed by the software running on the embedded processor. Since modelling and simulation of complex ASIC with C/C++ models becomes more and more important and is already code of practise at many design centres of ASEL, power estimation and optimisation at this level is a key issue for making early trade-offs and an optimal HW/SW partitioning. As low power is a critical issue for all current and especially future designs, ASEL intends to drive the development and exploitation of tools in that area to make sure that actual and future requirements will be met. The developed tools and methodologies will be used in power critical projects to overcome the lack of commercial solutions. Furthermore ASEL will be able to spread the methodologies to other design centres via his processor platform.

ARM will apply the POET tools and methodology to the design characterisation of SoC designs which include an on-chip cache-based processor (as is typically found in most such designs). The implementation of the cache architecture and operation can have a substantial impact on the overall system power consumption – cache size and depth and hit/miss rates, write-buffering type and fetch block size, and cache-flushing decisions all impact the overall system power consumption, silicon area and performance to a considerable degree. In fact, non-optimal cache design can impact both performance and power consumption to a much greater degree than non-optimised core processor design alone. The POET approach will be used in later stages of the project to synthesise real applications with varying elements of cache architecture and implementation, to characterise the consequences for power consumption and performance in each instance. Application of these outcomes will then be used to optimise the design rules for cache architectures to achieve the best balance between the different requirements specified for the system.

# 6. Community added value and contribution to EU policies

The POET project proposal addresses the key vision statement of the IST 2000 workprogramme:

"Start creating the ambient intelligence landscape for seamless delivery of services and applications in Europe relying also upon test-beds and open source software, develop user-friendliness, and develop and converge the networking infrastructure in Europe to world-class".

The key enabling technologies for this vision are a wireless network infrastructure and the powerful mobile communication and computation terminals. Several of the WP2000 priorities to realise the vision are directly addressed by the POET project:

To improve natural and personalised interactions with IST applications and services. This includes multi-lingual/multi-modal interaction systems that are adaptable to the user's preferences and lifestyle (e.g. sensitivity to gender, age and culture).

To foster the development and convergence of networking infrastructures and architectures including the integration of fixed, mobile, on-line and broadcasting technologies.

To develop embedded technologies, their interconnections and their full integration into the service infrastructure, the workplace and business processes. To develop applications and services that take advantage of such systems.

To reconsider service provisioning in the context of any-where/any-time access to services and ambient dialogue modes including public services and, mediation and commercial transaction systems.

Further the proposal targets other objectives which strengthen the European industry and economy:

It promotes the take-up of methodology and tools in industrial environments, by solving problems and bottlenecks in several application domains.

It supports the development of design techniques that are useful and applicable to several application domains, in particular consumer and communication systems.

It contributes to the dissemination of such technologies to small, medium and large European companies, by offering direct marketing channels in Europe.

The vital importance of embedded systems for the telecom infrastructure has been generally acknowledged in the market. In our opinion, the project will substantially contribute to the implementation and evaluation of the above-mentioned objectives through the development of methods and tools to be used in the design of Systems-on-Chip (SoC).

The power consumption of SoCs is one of the main limitations of the integration of additional functionality. It has a massive impact on the reliability, power delivery, heat dissipation, package cost and battery life time. Hence means to reduce the power consumption of embedded SoCs have been identified as high priority research topics by the Int. 1999 SIA Technology Roadmap, the EDAA Design Technology Roadmap and by the CEC in the IST programme as well as by the special action ESD-LPD.

The embedded SoCs in communication systems (network and terminals) are complex architectures consisting of DSPs, µ-Controllers, memories, interconnect and dedicated hardware. Existing work on power reduction of these systems started at the component level by performing local optimisations. It is obvious that these optimisations cannot result in an overall optimised architecture. Attempts to start optimisation at the algorithm level for the software part have so far only been done on p-code or assembler level. Optimisations of behavioural descriptions of the hardware part and at the register transfer level are unique world wide. To tackle this challenge requires to focus the design scope and solution space to the most relevant application domains in the European market. The effort that is required for this proposal is suited for a project of European dimension. In fact, no single entity in one country could support the tasks of formalising, developing, promoting, AND applying the required methodology. Further in a previous EU-funded project the kernel of the consortium has very successfully demonstrated its good co-operation and the potential to develop low power tools driven by the specialised needs of some major European system houses.

NOKIA, the world wide market leader in wireless communication and Siemens ICN, a leading provider of network equipment have expressed their strong interest in this project and assured to help in the definition of the requirements and in the evaluation phase in a less formal way.

# 7. Contribution to Community social objectives

By providing an improved technology this proposal will contribute basically to improving employment availability of consumer products.

Unemployment is one of the key factors that needs to be reduced in the near future. In the last year, not only the less industrialised countries of the Community, but also the major and more developed ones, have suffered from high unemployment rates. Reducing unemployment requires maintaining a competitive edge of European products. Microelectronics and telecom are among the main industrial resources of the European Community and must be supported with this goal in mind.

Furthermore, according to a study conducted by GMM, the Microelectronics and Microsystems group of the German EE society, the semiconductor percentage content in consumer products will grow from 16% in 1999 to 22-30% in 2003. This growth implies that competitiveness in consumer products will become highly dependent on microelectronics development. Roughly speaking, each microelectronics employee influences 50-100 employees of the microelectronics client industries.

This will consequently favour the increase of the employment of young engineers and common labourers in existing design and production sites and will support the development of small and medium enterprises able to provide highly-specialised and niche services to the large companies involved in such design and implementation requirements.

Furthermore, market growth analysis shows that this project will especially benefit the semiconductor industries in Europe. In the competitive area in general purpose processors and peripheral chips, Europe has lost some ground in comparison with US and the Far East. However it is claimed that Europe is quite strong in the fields of ASICs (application-specific integrated circuits), algorithms and SW, as well as in system engineering. Due to the fact that most advanced algorithms and functionality in embedded systems will be carried on by ASICs, the market share can be increased by methodology and tools able to provide faster solutions and better quality of performances. Mobile and multimedia applications are expected to grow also considerably in the near future. Specifically it is claimed that data will account for 30% of network operators' revenue within two years. Due to the expected market expansion in this domain, microelectronic design improvements provided to European companies will allow an expansion of production and a resulting increase of the employment in these advanced sectors of society. ICE (Integrated Circuit Engineering) magazine 1998, predicts an average annual growth rate for the period 1997-2002 of 20% for ASICs and of 31% for Standard Cells, with a turnover (Bill. \$) of 8.0 and 33.9 respectively, world-wide in 2002. The growth of telecommunication/industrial/consumer applications will be faster than that of computing. The support for these sections of the industry needs to be lead by Europe since it is where European strength lies.

Moreover these data prove that a turnover in microelectronics will enable a value addition in high level products, in particular in the European key industrial areas. It thus will enable employment in these domains. The design technology, methodology and tools developed in this project will also enhance the quality of life in several areas. New families of information technology products will be created and sustained in the areas of communication, consumer electronics, healthcare, information appliances, automotive electronics etc., promoting the ease by which citizens manage their everyday affairs. Furthermore, due to the significant potential of cost reduction that will be achieved using the accelerated design cycle, the aforementioned products will be made accessible to multitudes of citizens. Finally, these products will feature an enhanced quality and safety, due to the reusability of proven parts facilitated by our design methodology.

These economical and social opportunities, however, do not come for free. E.g. at this year's  $CO_2$  conference in Amsterdam it was stated that:

20% of the electrical energy around Amsterdam is used for telecom. In the US the internet is responsible for 8 to 9% of the total electricity consumption, including all computer applications this percentage grows to 13%. It seems reasonable to predict that within two decades 30 to 50% of the nation's electricity.

It seems reasonable to predict that within two decades 30 to 50% of the nation's electricity supply will be required to meet the direct and indirect needs of the internet.

The transfer of 2,000 Kbytes of data through the net consumes the energy of a pound of coal.

While the information and communication society saves a lot of fossil energy because it avoids moving physical objects and reduces travel, it consumes a significant amount of energy itself. Hence besides the positive impact on the competitiveness of the European communication industry and the aforementioned impact on employment, the POET project helps to reduce the energy consumption of the information society and hence helps to protect our environment.

# 8. Economic development and S&T prospects

As explained in detail in the description of WP 7 of this Annex, the different exploitable results of this project will be:

A seamless design methodology for low power Systems-On-Chip (SoC) ranging from system level down to the RT-Level, that could be integrated in the co-design flow (if any) of any European electronic or telecom company.

A consistent suite of analysis, estimation and optimisation tools for different levels of abstraction in the design of low power SoCs.

A number of designs case studies done by the industrial partners leading to an evaluation report on the tools.

The specificity of our tools and their implied methodology will be of prime importance for a good market position of the future products.

## 8.1. Market Position

## 8.1.1. General Trends of the EDA Market (system and RT level)

EDA industry exhibits an average growth rate of 20.8 % per year, with strong discrepancies between subdomains: system level grows much faster (27.2 %), while traditional gate level design exhibits only 8% growth. This is still a global average. When going into more details, some specific tools are now on the decline (schematic capture, fault simulation). An interpretation to this may be that there is a very strong demand, facing a reasonably mature offer for design entry and simulation, while the offer for behavioural synthesis is still below customer's expectation. This means that there is room for new products in this field, even in a market that is strongly dominated by big companies (50% Synopsys, 30% Mentor).

#### 8.1.1.1. Electronic System-Level (ESL) Methodology

In the SoC industry currently a shift towards system level design is noticeable. The discussions on C-based design is an obvious indicator. The technical and commercial background behind this move is threefold:

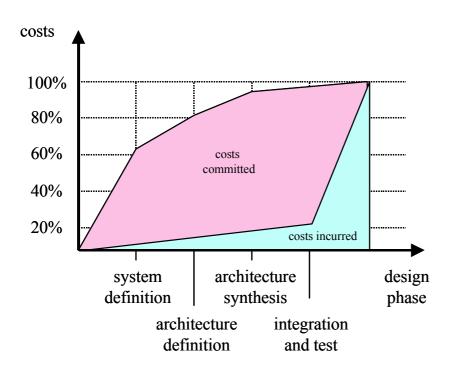

The total cost and performance of a system is primarily determined by the early design decisions done at system level, i.e. the algorithm selection and optimisation as well as the architecture definition. Figure 2 illustrates the relation between cost commitment and cost incurred during the design phases of a SoC. It is remarkable that the potential for cost and performance optimisation is very low at the late design phases.

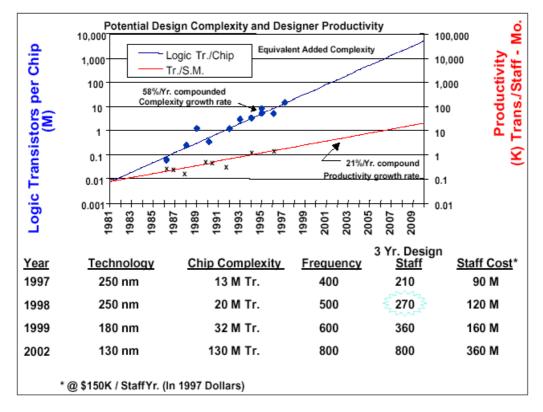

The gap between technology improvements and design efficiency over time forces to concentrate on higher levels of abstraction. Figure 3 shows the respective chart of the 1999 Int. SIA Technology Roadmap. The move to higher levels of abstraction has taken place at similar situation in the past when cell based design and logic synthesis had been introduces. Finally related to the increase in complexity, the performance of tools of lower levels is insufficient to handle very large designs.

Finally related to the increase in complexity, the performance of tools of lower levels is insufficient to handle very large designs.

Figure 2: Cost commitment over design time.

These conclusions are supported by DataQuest market predictions. From the DataQuest ESL methodology classification, the following are relevant for the POET proposal:

Electronic System Level Design (ESLD) Behavioural synthesis Emulation and acceleration

The ESLD itself covers architecture synthesis and related tools. ESLD and behavioural synthesis and formal verification are "big hopes", however, present solutions are not yet mature enough, and predictions are highly questionable. The market may grow much faster if more mature solutions are introduced (See Table 1 for details).

| M US\$ 1                       | 1997 | 1998  | 1999  | 2000  | 2001  | CAGR % |

|--------------------------------|------|-------|-------|-------|-------|--------|

| ESL                            | 84.7 | 107.5 | 137.2 | 174.9 | 223.6 | 27.2   |

| ESLD                           | 42.3 | 50.8  | 60.9  | 73.1  | 87.8  | 20     |

| Behavioural Synthesis          | 9.6  | 13.1  | 16    | 24.7  | 33.9  | 37.5   |

| ESL Emulation and Acceleration | 0.6  | 1.2   | 2.4   | 3.2   | 4.1   | 67     |

Table 1: Annual Turnover for EDA software by methodology

POET clearly targets at an increasing share of the EDA market, namely the ESLD market. The predicted growth in emulation and acceleration is a hint on the performance bottleneck in

Figure 3: Design Gap (source: 1999 Int. SIA Technology Roadmap)

high level design evaluation and validation. No tools for power consideration at this level are on the market yet, hence POET clearly addresses a promising market niche.

#### **RTL Methodology**

RTL methodology was profoundly revisited under the pressure of sub-micron technology requirements. The dominant effect of wire delays and all other parasitic effects (electro-magnetic interference, metal migration, thermal problems) has pushed for a better link between RTL synthesis and library mapping with back-end related issues. Power is now an optimisation criterion as important as performance. A second issue is related to design methodology: embedded systems require appropriate facilities for HW/SW co-design. This has a direct influence on RTL design tools (co-simulation, RTL virtual prototype - emulation).

| M US\$                             | 1997  | 1998  | 1999 | 2000  | 2001  | CAGR % |

|------------------------------------|-------|-------|------|-------|-------|--------|

| RTL                                | 697   | 896   | 992  | 1258  | 1585  | 23.1   |

| RTL Design                         | 28.7  | 35.8  | 39.7 | 44.1  | 49    | 13.7   |

| RTL Simulation                     | 303.4 | 368   | 404  | 484   | 574   | 18.5   |

| RTL Synthesis                      | 207.8 | 251.3 | 271  | 330.2 | 396.2 | 18     |

| Target Compiler (layout generator) | 9.4   | 16.7  | 20.9 | 26.1  | 32.6  | 34.1   |

| DFT                                | 50.2  | 51.5  | 57.7 | 83.7  | 121.3 | 28.5   |

| Design Emulation and Acceleration  | 67.5  | 105.9 | 108  | 153.4 | 217.8 | 34     |

| RTL Virtual Prototyping            | 5.8   | 10.6  | 11.2 | 23.9  | 31    | 44.3   |

| RTL Analysis (power, timing,)      | 39.7  | 56.3  | 79.9 | 113.8 | 162.7 | 42.1   |

Table 2: Annual Turnover for EDA software by RTL design task

As one can see in Table 2, one of the largest increases in turnover is expected to be in RTL analysis tools, in particular for low power.

## 8.1.2. Current Offer Low Power Tools at RT and Algorithm Level

In the following, we briefly review the relevant tool developments concerning high-level power optimisation. Given the context of the project, tools addressing the logic level and below will not be considered.

#### Software Level

Software power estimation techniques operating at different levels of abstraction have been proposed. Most of the approaches analyse the code at assembly level relying on an RT- or behavioural-level model of the microprocessor. These methods suffer two major drawbacks: the need of an accurate description of the microprocessor core and extremely long simulation run times. Recently, these problems have been partially overcome by focusing on an abstract (functional) model of the processor. Prototype tools implementing this technique have been developed within the PEOPLE project. The toolset provides core characterisation and assembly-level software estimation capabilities. No reliable and widely applicable strategies working at source-level have been proposed in literature and no commercial or prototype tools are currently available.

Concerning the power optimisation, many proposals focused on reducing the power consumed by memories, trying to minimize the need to access main memory through a careful management of data organisation, while exploiting the presence of caches. Other techniques operate at the instruction-level, and are based on a proper modelling of the microprocessor to provide power figures for each instruction. Power optimisation is then accomplished by selecting the best mix of instructions to execute the given application. A few techniques, still working on the code, for specific classes of applications can reduce power

demand by decreasing the accuracy of computation within the limit of tolerability. Dynamic variable-voltage techniques have been also proposed, to reduce performance and power consumption, during the execution of weakly critical sub-tasks. Dynamic power management can be also employed at system level, by means of a suitable methodology forcing (sleep) low power states, when the system becomes inactive; both fixed and predictive strategies have been proposed.

Hence, the task of managing the software-specific power-issues is not yet shifted toward EDA vendors. In particular, there is a lack of methodologies and tools working at source level both for estimation and optimisation of power consumption.

#### Algorithm Level

The research and development centre IMEC, Belgium, has developed a system level synthesis tool called Matisse. Matisse transforms a concurrent object-oriented system description into synthesisable hardware respectively compilable software descriptions. The focus of the design space exploration in Matisse is on the memory management and the memory architecture. Power models of the memories and the memory managers are applied. However, only constant external I/O load is assumed which limits the accuracy of the estimated communication cost. The power consumption of the address generating logic is not considered.

ATOMIUM, another tool from IMEC, allows a design space exploration for data storage and transfer dominated multimedia designs written in C/C++. Also in this tool, the power consumption of the memories is included in the cost function but all other power contributors are not taken into account. Basically, power is minimised by removing redundant memory accesses and splitting memories to avoid multi-port memories.

The Behavioural Compiler from Synopsys allows insertion of clock gating logic while compiling a behavioural description to the structural RTL level. Other power optimising features are not included.

PowerBuster-D from ASC synthesises behavioural HDL designs into structural RTL with the objective of minimizing power consumption under a performance constraint. Area of the design can be treated as either a constraint, or an optimisation parameter, along with power. The tool can also determine the optimal clock period for the design. PowerBuster produces and RTL datapath instantiating selected RTL library components, and an FSM controller for the datapath. The output of PowerBuster-D is compatible with popular RTL synthesis tools. This project is developed in collaboration with a university and seems to be stopped. It may restart in the future if a new partner gives founding for new development and industrialisation of the tools. The level of beta support evaluation is unclear at the moment. It is not clear which synthesisable sub-set PowerBuster supports.

#### **Register Transfer Level**

Power Compiler from Synopsys addresses power optimisation at the RTL by resorting to two distinct techniques: Clock gating and operand isolation. Clock gating circuitry, although automatically inserted in the RTL description, is only exploited during RTL-to-gate compilation; therefore, it can not be seen as a pure RTL optimisation solution (synthesis is required). Operand isolation can not be considered as an automatic RTL transformation, at least in its current implementation within PowerCompiler. In fact, the designer is required to manually identify the data-path blocks whose operands should be isolated and to mark them with pragmas in the VHDL/Verilog code, so that during synthesis useless computations are avoided. The most sophisticated and effective optimisations supported by PowerCompiler take place at the gate-level; therefore, PowerCompiler cannot be considered a real competitor of the RTL optimiser that will be developed within POET, whose target is rather the cycle-accurate RTL.

WattSmith from Sequence identifies power optimisation opportunities at the functional RT level. Optimisation opportunities like ignored memory reads or explicit clock enables which might be replaced by a gated clock are detected. WattSmith can thus be considered as an "advisor" for the designer; in other words, its main purpose is that of pointing out to the designer what kind of optimisation can be applied to some blocks of the description; however, a lot of human intervention is required to perform the optimisation capabilities. Furthermore, it will exploit more innovative (and potentially effective) techniques for power minimisation ("local" optimisations, such as those proposed by WattSmith, will be paired by more "global" optimisation, e.g., synthesis of the memory hierarchy, including caches, systems bus interfacing, global power management).

# 8.1.3. POET's Unique Feature: A Seamless Low Power SoC-Design Flow

System-on-Chip (SoC) design flows, as they are applied by many design companies, commonly start with a C/C++ executable specification of the system's functionality. An indepth analysis of the specification is carried out to get a rough estimate of the timing behaviour as well as area and power requirements. Based on these estimates, the system description is partitioned into software and hardware parts. The software parts are mapped onto processors and DSPs while the hardware part is synthesised to a gate level netlist. Timing and overall system cost are the driving metrics for this partitioning step.

After partitioning, the POET low power optimisation methodology is applicable. This methodology will be realised by a set of new design tools. The software power optimisation flow transforms the software specification into a functional equivalent description. The resulting description is optimised with respect to the required energy consumption to execute on a given processor architecture including the memory sub-system. Traditional compilation finishes this part of the design flow.

The hardware specification is optimised for its power consumption at two different levels of abstraction in order to benefit from all effective optimisation design tricks. At the algorithm level, the hardware specification is first transformed similar to the optimisation step at the software side. However, the hardware transformations have a different cost metric behind. These transformations are mainly interconnect driven because interconnect cost tend to dominate the overall hardware power cost. The second design step at the algorithm level is synthesis to the register transfer level of abstraction. This high-level synthesis task is supported by the POET design flow in that low power scheduling, allocation, and binding constraints are generated.

Finally, fine-grained power optimisations at the RT level are performed which address communication interfaces, power management, and the memory hierarchy. Logic synthesis and place and route, being outside the scope of POET, are the remaining design steps.

# 8.2. Consortium Exploitation plan

A workpackage (WP) has been identified with the purpose of defining and initiating the exploitation of the project results by the consortium (see description of WP 7 in Part B of this proposal). As the EDA company of the consortium, OSC, will be responsible for the management of this WP. The exploitation effort will be undertaken by all of the partners, each with their specific interests and missions:

The end-user companies, ASEL, and ARM will internally use the methodology and tools defined in this project, and will contribute to the external promotion of the project by publishing their experience as users.

The industrial partner ARM will utilise the tool developments to strengthen its offer in design support for low power applications.

The EDA company OSC, together with the subcontractor BullDAST, will assure the external promotion of the tools developed within this project, and will define a strategy to industrialise and market EDA products based on these tool prototypes.

The research institutes OFFIS, Politecnico di Torino and CEFRIEL will actively support the external promotion of the methodology and tools of this project by presenting papers and contributing to demos of prototype tools at various conferences and exhibitions. Associated industrial parties include Siemens ICN and Nokia will evaluate the results and if efficient will internally exploit them. See the included letters of interest at the end of this document.

As detailed in the description of WP 7, the important milestones for the consortium exploitation will be the tool demonstrations during EDA conferences and exhibitions, such as the Design Automation and Test in Europe (DATE) conference and exhibition, the Asian-Pacific-DAC (ASP-DAC) exhibition and conference in Asia and possibly the Design Automation Conference (DAC) in the US. Other common promotion actions, such as publications and WWW advertising, will be undertaken during the project. The estimated costs of these exhibitions and actions for OSC are stated in "Other Specific project Costs" on form A4.

Politecnico di Torino, CEFRIEL and OFFIS have a history of successful joint collaboration, especially in the area of low power design and tools. This co-operation will be extended to the spin-offs OSC and BullDAST. Respective co-operation agreements between the institutes and their spin-offs are in place.

This unique synergy and close co-operation between EDA vendors and research institutes will permit the full exploitation of the project results at the different levels mentioned above. The research institutes will promote the new low power design methodology, as well as the tool suite, by publishing articles in international conferences and organising tutorials on the tools. OSC and BullDAST will use their existing links into industry to directly market and build up new links directly and through joint marketing agreements as well as through international distributors to market the tool suite.

# 8.3. Individual Exploitation plans

The project is clearly driven by industrial partners, each of them investing 50% of the project cost from their own budget. It is hence the prime commercial objective of each partner, to receive a return on their investment as soon as possible. The appearance of this return, however, may be of a completely different nature for each partner. In some cases, the project results will put the partner in a favourable position with respect to the competition because of the experience with and access to advanced design technologies and tools. In other cases, the designed prototypes will be directly engineered into marketable products, e.g., for the EDA market. Finally, the results may be exploited as a starting point for future research activities or key technology for spin-off companies. The following sections describe the individual exploitation plans and expectations for each partner.

# 8.3.1. OFFIS

Since direct marketing of tools is beyond the scope of OFFIS, being a non-profit research institute, OFFIS will rely on OSC as a marketing channel of the tool set. OFFIS will transfer the know-how and the right for non-exclusive unlimited exploitation under a licensing agreement with OSC to allow them to market the POET tools. This exploitation channel is actively supported by OFFIS technology transfer activities as outlined below.

In the previous PEOPLE project, OFFIS has developed prototype tools for power estimation at the behavioural level. These tools have been packaged together with power estimation of memory usage and power characterisation tools as well as with a graphical user interface under the registered trade mark ORINOCO<sup>®</sup>. Parts of the ORINOCO<sup>®</sup> algorithms have been

registered for patent. For OFFIS as a research institute, the consolidation of its low power design technology and amendment by optimisation tools as well as the feed back from industrial applications on the feasibility, the efficiency and the limitations is very important.

By developing, implementing and maintaining the ORINOCO<sup>®</sup> tool suite, OFFIS pursues the following objectives:

The know-how of low power SoC design and optimisation will be integrated into courses at Oldenburg University, which is closely connected to OFFIS (e.g., lectures on embedded system design). In this way, students will have the opportunity to get in touch with this new modelling paradigm.

Similarly the know-how will be integrated into low power design courses offered at the OFFIS Training Centre (OTC) possibly in close marketing co-operation with the Mikroelektronik Akademie, Hannover, a subsidiary of the former Sican Design Centre.

Usage of the experience and tools in the OFFIS Design Centre (ODC) which is currently being founded. The target application domain of ODC is low power communication systems, for which power optimisation is crucial. Hence OFFIS aims at putting itself into a favourable position also in the design service business by applying the results of the POET project including the whole POET low power design flow.

Consolidation of OFFIS as a competence centre for design methodology and tools for low power SoCs.

To reach this objective, OFFIS actively publishes and promotes its low power technology. In recent years ORINOCO<sup>®</sup> has been presented at several international conferences and exhibitions (e.g., ISLPED'99, ISLPED'2000, DATE'99, DATE 2000, DAC 2000). OFFIS has begun to organise hands-on workshops in order to give the participants an idea of the benefits and quality of the ORINOCO<sup>®</sup> tools. These activities will be continued in the future.

OFFIS relies on OSC to market the ORINOCO<sup>®</sup> power estimation and optimisation tools.

## 8.3.2. ASEL

ASEL is working in the area of very advanced, high complexity ASICs. Thus low power is expected to be a crucial issue for all future activities. ASEL intends to drive the development and exploitation of tools in that area to make sure that actual and future requirements will be met. The developed tools and methods will be used in power critical projects to overcome the lack of commercial solutions.

The company foresees that power will be a crucial factor in the design and implementation in new generation ASICs (Systems on silicon). For this reason ASEL feels that is of enormous importance to utilise the estimators and optimisers developed in the POET project. The exploitation of the results during POET Project life-span will be the application of the tools to the design of a complex device. Some simpler modules will be considered as benchmark to provide feedbacks to the developers. The complexity of the device will be representative of ASEL's internal needs. The benefit and advantages offered by the technology will be evaluated thoroughly. After a positive testing and acceptance of the tools, internal qualification will be granted. In this case the exploitation will proceed after the end of the project with the integration of the tools in ASEL proprietary design flow. Furthermore ASEL will organise seminars and training courses regarding power estimation and optimisation to improve the internal dissemination process. The commercialisation of EDA tools being outside the strategic commitment of the Company, no policy will be applied in this field.

## 8.3.3. ARM

The Low power design tools developed in the POET project will enable current and planned ARM architectures to achieve the performance requirements of current and future mobile applications. It will generate incremental revenue for ARM through allowing it to address new markets, produce cost reduced versions of existing applications and to develop higher performance, next generation applications. As a leading provider of microprocessor core for power sensitive applications it is vital to enable designers to evaluate both processor and system architecture choices and their impact of final system power before committing to silicon. As the complexity of designs increases the ability to perform these complex calculations requires tools support. The availability of these tools is therefore critical to ensure the successful implementation of ARM based design and hence the profitability of ARM.

# 8.3.4. CEFRIEL

CEFRIEL being a research centre subcontracts the promotion and commercial exploitation of their prototype tools to BullDAST. CEFRIEL will do dissemination of the results of the project through several channels in order to provide the maximum international visibility to the achievements. Technical articles and presentations during international conferences and workshops addressing system-level design and low power issues will be provided (as happened for the PEOPLE project), with some extent during exhibits in which OSC/BullDAST will have a booth. Seminars and training initiatives will be triggered to get feedbacks and promote the use of our tools and methodologies by including it as part of the Master Program in Information Technology provided by CEFRIEL, that is also open to designers coming from the over 20 main industries sponsoring CEFRIEL, representing the major players in the field of Communication and Information Technology. This will represent an additional important vehicle to promote and consolidate the relationships with such industries and to directly show, with the necessary extent, the potential benefits of the POET methodologies and tools directly to the industrial end-users.

## 8.3.5. OSC

Being a system level EDA vendor for embedded systems, OSC will naturally concentrate its exploitation efforts on the software technology and the tools developed within the project, i.e., the SW-power-estimator and optimiser (developed by CEFRIEL), ORINOCO<sup>®</sup> (developed by OFFIS), and the RT-level power optimiser (developed by Politecnico di Torino).

The business unit "Embedded Systems" in OSC is currently offering a suite of tools for formal verification of embedded systems. These tools originate from research at Oldenburg University and OFFIS. The tools have been transferred for exploitation to OSC under a co-operation and licensing contract. OSC is responsible for the further development, integration, support, training and marketing of the verification tools. The marketing is done through a joint marketing agreement with i-Logix, the vendor of the Statemate and Rapsody tools. Customers of the OSC verification tools include: BMW, Daimler Chrysler, General Motors, Nissan and PSA.

This agreement and marketing strategy is a model for the exploitation of the POET tools.

OSC is currently extending its portfolio of products by tools for system level design of communication systems. OSC is preparing the marketing of the ORINOCO<sup>®</sup> tools, which will be licensed from OFFIS and industrialised. The ORINOCO<sup>®</sup> tools have been presented at DAC'99, at DAC 2000, at DATE 2000 and at the Int. Symposium on Low Power Electronics and Design (ISLPED) 2000. During these demos they gained a lot of interest which led to onsite presentations at Bosch, IMEC, Infineon, Nokia and Philips. Currently evaluations are being performed at IMEC, the ORINOCO<sup>®</sup> technology is in use at Bosch other evaluations are

scheduled for early 2001. At the 38<sup>th</sup> DAC, June 2001, ORINOCO<sup>®</sup> will be shown at the joint OSC / OFFIS booth.

In view of the predicted growth of this market segment and the fact that the POET tools cover the entire system level low power design flow in a new and seamless way which is currently without any competition on the market place, OSC "Embedded Systems" expects to increase its revenue by several millions of EUROs by addressing the communication industry and selling licenses to the major players.

## 8.3.6. Politecnico di Torino

As a public university, Politecnico di Torino is not in the position of marketing and industrially exploiting the results of any research project. For this reason, a spin-off company (BullDAST) has been established in year 2000 with the major purpose of turning into products the prototype EDA tools that have been developed over the years by the EDA group. BullDAST will support OSC in the commercial exploitation of the POET results which are directly related to the activities covered by Politecnico di Torino.

The main contribution of Politecnico di Torino to the exploitation of the POET project will be on the dissemination of the achieved research results through technical presentations at international conferences and workshops, technical articles in the major journals and magazines addressing system-design and low power design issues, participation to fairs and exhibits such as those held at DATE, DAC and ISLPED, lectures and seminars in the context of international schools (e.g., Master programs in European universities, NATO summer schools) and training initiatives (e.g., EuroTraining courses).

Similar dissemination has distinctively characterized the exploitation activities carried out by Politecnico di Torino within the PEOPLE project. A total of 13 journal/conference articles (including contributions on IEEE Trans. On VLSI Systems, DAC: Design Automation Conf., ICCAD: Intl. Conf. On CAD, ISLPED: Intl. Symp. On Low Power Electronics and Design) have been published on subjects directly related to the results achieved in PEOPLE. Most of the research findings from the project are also included in the list of contents of the course: "Design Techniques and Tools for Low power Digital Systems" that is part of the EuroTraining catalogue and that is held twice per year at the italian site (i.e., COREP, Torino) of EuroTraining.

Concerning internal exploitation, Politecnico di Torino will benefit from its own research carried out within the POET project, as well as from that performed by the other partners (both research institutes and industries), to consolidate its know-how and expertise on high-level low power design methodologies. Politecnico di Torino holds a leading position world-wide in this specific area, as demonstrated by the scientific production of its faculty and affiliated researchers, as well as the number of cooperations and technical consulting it is currently undertaking. Among the companies that are, at this point in time, carrying out joint research with Politecnico di Torino, there are most of the major players of the semiconductor (i.e., ST Microelectronics, Infineon, Intel, National Semiconductors, Samsung Electronics), system/telecom (i.e., Philips, Siemens ICN, Intracom, Hewlett-Packard, Omnitel, Telecom Italia, Infostrada, CSELT), software (i.e., Microsoft) and EDA (i.e., Synopsys, Cadence) scenarios. The POET project will offer to Politecnico di Torino a unique opportunity for consolidating its relationship with the aforementioned companies, as well as for creating new links and contacts with other important actors of the ICT arena.

# 9. Workplan

# 9.1. General Description

The following organisation is a mean to achieve the high-level objectives of the project:

Define a consistent and general methodology for power estimation and optimisation of embedded HW/SW systems.

Improve and implement the necessary tools to enable the developed methodology. Evaluate the methodology and tools.

Quantify the achievements based on user input.

Enable sustained commercial tool exploitation.

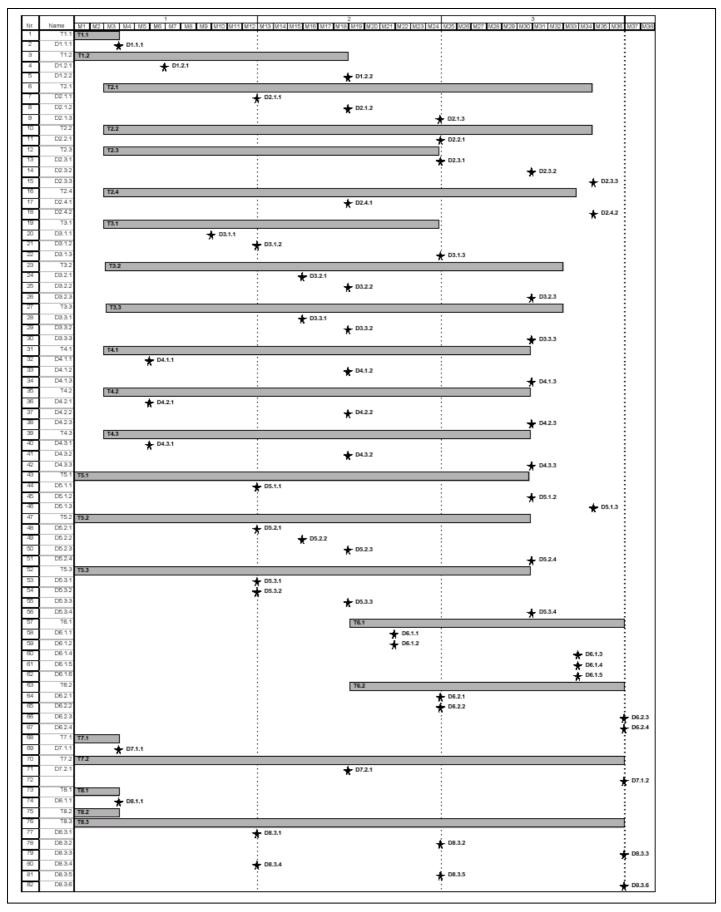

The objectives of the project will be achieved by joining the forces of Europe's leading communication and embedded processor industries with well established research centres for low power design and methodologies. However, the objectives stated are very ambitious and could certainly not be achieved without being able to build on previous results and experiences from an earlier co-operation of the kernel set of partners (OFFIS, CEFRIEL, POLITO, ASEL and ARM). During this earlier project which had been rated very positively by the commission, the reviewers, and the partners themselves, the consortium could not only demonstrate its good co-operation, but also excellent scientific and engineering results. These will be brought into the POET project as background information.